# Abstract Single-Chip Smart Sensor QMS7926

Advanced Information

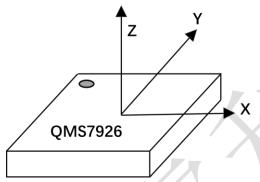

QMS7926 is a highly integrated intelligent sensor chip, which are packaged in BGA60,4x4x1.2mm3. Its built-in main functional modules include: high precision and low power consumption triaxial acceleration sensor and signal processing circuit, ARM M0 kernel microprocessor, 2.4G RF transceiver / Bluetooth BLE broadcast module and so on.

- Key Features

- 3-Axis Accelerometer with low noise, high accuracy, low power consumption and offset trimming

- Up to 48Mhz ARM® Cortex™-M0 32-bit processor

- 2.4 GHz Bluetooth Low Energy (BLE) transceiver

- Supply voltage range 1.8V to 3.6V

- 3-Axis Accelerometer

- 14-Bit ADC with low noise accelerometer sensor

- High resolution allows for motion and tilt sensing

- I2C Interface with Standard and Fast modes

- low power consumption (2-50uA low power conversion current)

- Automatically maintains sensor's sensitivity under wide operation voltage range and compatible with battery powered applications

- ◆ ARM® Cortex™-M0 32-bit processor

- Memory

- > 512KB in-system flash memory

- ➤ 128KB ROM

- 138KB SRAM, all programmable

#### retention in sleep mode

- 31 general purpose I/O pins

- All pins can be configured as serial interface and programmable IO MUX function mapping

- > All pins can be configured for wakeup

- 16 pins for triggering interrupt

- 3 quadrature decoder (QDEC)

- > 6-channel PWM

- 4-channel I2S

- 2-channel PDM

- 2-channel I2C

- 2-channel SPI

- 1-channel UART

- JTAG

- 6-channel 12bit ADC with analog PGA

- 4-channel 32bit timer, one watchdog timer

- Real timer counter (RTC)

- Power, clock, reset controller

- Flexible power management

- Supply voltage range 1.8V to 3.6V

- Embedded buck DC-DC

- Embedded LDOs

- Battery monitor: Supports low battery detection

- 2μA @ Sleep Mode with 32KHz RTC

- > 0.7μA @ OFF Mode (IO wake up only)

**Document #:** 13-52-18 **Title:** QMS7926 Datasheet

Rev: A

- ◆ 2.4 GHz Bluetooth Low Energy (BLE) transceiver

- 2.4 GHz transceiver

- Compliant to Bluetooth 5.0, ETSI EN 300 328 and EN 300 440 Class 2 (Europe), FCC CFR47 Part 15 (US) and ARIB STD-T66 (Japan)

- > Sensitivity:

- -97dBm@BLE 1Mbps data rate

- -103dBm@BLE 125Kbps data rate

- TX Power -20 to +10dBm in 3dB steps

- ➤ Receiver: 8mA @sensitivity level

- Transmitter: 8mA @0dBm TX power

- Single-pin antenna: no RX/TX switching required

- RSSI (1dB resolution)

- RC oscillator hardware calibrations

- 32KHz RC oscillator automatic calibration

- 32MHz RC oscillator automatic calibration

- AES-128 encryption hardware

- AES-ECB

- > AES-CCM

- Link layer hardware

- Automatic packet assembly

- Automatic packet detection and validation

- Auto Re-transmit

- Auto ACK

- Hardware Address Matching

- Random number generator

- Operating condition

- Supply voltage range: 1.8V to 3.6V

- Operating temperature: -40°C to 85°C

- ◆ RoHS Package: BGA-60

18

Title: QMS7926 Datasheet

Rev: A

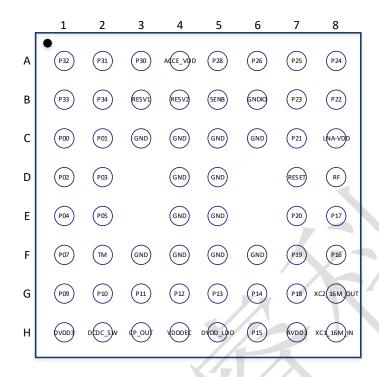

## Pin Assignment

## **Pin Configurations**

| Pin Number | Pin Name | Description                                                            |  |  |  |  |

|------------|----------|------------------------------------------------------------------------|--|--|--|--|

| ۸1         | D22      | all functions configurable                                             |  |  |  |  |

| A1         | P32      | *Note: Not support interrupt and ADC function                          |  |  |  |  |

| A2         | P31      | all functions configurable                                             |  |  |  |  |

| AZ         | h21      | *Note: Not support interrupt and ADC function                          |  |  |  |  |

| A3         | P30      | all functions configurable                                             |  |  |  |  |

| AS         | P30      | *Note: Not support interrupt and ADC function                          |  |  |  |  |

| A4         | ACCE_VDD | power supply of Accelerometer                                          |  |  |  |  |

| ۸Ε         | D29/CDA  | it is connected between P28 of MCU and SDA of Accelerometer internally |  |  |  |  |

| A5 P28/SDA |          | *Note: Not available for other signals.                                |  |  |  |  |

| A6         | P26/SCL  | it is connected between P26 of MCU and SCL of Accelerometer internally |  |  |  |  |

| At         |          | *Note: Not available for other signals.                                |  |  |  |  |

| A7 P25     |          | all functions configurable/test_mode_select [1]                        |  |  |  |  |

| A/         | F23      | *Note: Not support interrupt function and ADC function                 |  |  |  |  |

| A8         | P24      | all functions configurable/test_mode_select [0]                        |  |  |  |  |

| Ao         | F24      | *Note: Not support interrupt function and ADC function                 |  |  |  |  |

| B1         | P33      | all functions configurable                                             |  |  |  |  |

| DI         | P33      | *Note: Not support interrupt and ADC function                          |  |  |  |  |

| В2         | P34      | all functions configurable                                             |  |  |  |  |

| DZ         | F 34     | *Note: Not support interrupt and ADC function                          |  |  |  |  |

| В3         | RESVE1   | reserved for Accelerometer                                             |  |  |  |  |

| в3         | KESVET   | *Note: Float or connect to GND                                         |  |  |  |  |

The information contained herein is the exclusive property of QST, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of QST.

Title: QMS7926 Datasheet

Rev: A

|    |              | T                                                                       |  |  |

|----|--------------|-------------------------------------------------------------------------|--|--|

| B4 | RESVE2       | Reserved for Accelerometer                                              |  |  |

|    |              | *Note: Float or connect to GND                                          |  |  |

| B5 | SENB         | protocol selection of Accelerometer                                     |  |  |

|    | 32142        | *Note: Connect to VDD                                                   |  |  |

| B6 | GNDIO        | test pin of Accelerometer                                               |  |  |

|    | GIVDIO       | *Note: Connect to GND                                                   |  |  |

| В7 | P23          | all functions configurable                                              |  |  |

|    | 7 2 3        | *Note: Not support interrupt function and ADC function                  |  |  |

| B8 | P22          | all functions configurable                                              |  |  |

| Во | r Z Z        | *Note: Not support interrupt function and ADC function                  |  |  |

| C1 | P00          | all functions configurable/JTAG_TDO                                     |  |  |

| CI | P00          | *Note: Not support ADC function                                         |  |  |

| C2 | P01          | all functions configurable/JTAG_TDI                                     |  |  |

| C2 | P01          | *Note: Not support ADC function                                         |  |  |

| C3 | GND          | Ground                                                                  |  |  |

| C4 | GND          | Ground                                                                  |  |  |

| C5 | GND          | Ground                                                                  |  |  |

| C6 | GND          | Ground                                                                  |  |  |

| 67 | B24          | all functions configurable                                              |  |  |

| C7 | P21          | *Note: Not support interrupt function and ADC function                  |  |  |

| C8 | LNA/TRX_VDD  | LNA and TRX VDD                                                         |  |  |

| D4 | P02          | all functions configurable/JTAG_TMS                                     |  |  |

| D1 |              | *Note: Not support ADC function                                         |  |  |

| D2 | P03          | all functions configurable/JTAG_TCK                                     |  |  |

| D2 |              | *Note: Not support ADC function                                         |  |  |

| D4 | GND          | Ground                                                                  |  |  |

| D5 | GND          | Ground                                                                  |  |  |

| D7 | RST_N        | reset pin                                                               |  |  |

| D8 | RF           | RF antenna                                                              |  |  |

|    |              | all functions configurable                                              |  |  |

| E1 | P04          | *Note: Not support ADC function                                         |  |  |

|    | 202 (200 = 1 | it is connected between P05 of MCU and INT1 of Accelerometer internally |  |  |

| E2 | P05/AINT1    | *Note: Not available for other signals and keep NC                      |  |  |

| E4 | GND          | Ground                                                                  |  |  |

| E5 | GND          | Ground                                                                  |  |  |

|    | λ            | all functions configurable/AIO<9>/Micphone bias output                  |  |  |

| E7 | P20          | *Note: Not support interrupt function                                   |  |  |

| E8 | P17/32K_OUT  | all functions configurable/AIO<6>/32k crystal output                    |  |  |

|    |              | all functions configurable                                              |  |  |

| F1 | P07          | *Note: Not support ADC function                                         |  |  |

| F2 | TM           | test mode pin                                                           |  |  |

| L  |              | '                                                                       |  |  |

The information contained herein is the exclusive property of QST, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of QST.

Title: QMS7926 Datasheet

Rev: A

| F3         | GND         | Ground                                                            |

|------------|-------------|-------------------------------------------------------------------|

| F4         | GND         | Ground                                                            |

| F5         | GND         | Ground                                                            |

| F6         | GND         | Ground                                                            |

| F.7        | D10         | all functions configurable/AIO<8>/PGA differential negative input |

| F7         | P19         | *Note: Not support interrupt function                             |

| F8         | P16/32K_IN  | all functions configurable/AIO<5>/32K crystal input               |

| C1         | D00         | all functions configurable                                        |

| G1         | P09         | *Note: Not support ADC function                                   |

| 63         | D10         | all functions configurable                                        |

| G2         | P10         | *Note: Not support ADC function                                   |

| G3         | P11         | all functions configurable/AIO<0>                                 |

| G4         | P12         | all functions configurable/AIO<1>                                 |

| G5         | P13         | all functions configurable/AIO<2>                                 |

| G6         | P14         | all functions configurable/AIO<3>                                 |

| <b>G</b> 7 | P18         | all functions configurable/AIO<7>/PGA differential positive input |

| G/         |             | *Note: Not support interrupt function                             |

| G8         | XC2_16M_OUT | 16M crystal output                                                |

| H1         | DVDD3       | 3V power supply for digital IO, DCDC, Charge pump                 |

| H2         | DCDC_SW     | buck dcdc output                                                  |

| H3         | CP_OUT      | charge pump output                                                |

| H4         | VDDDEC      | 1.2V VDD_CORE, digital LDO output                                 |

| H5         | DVDD_LDO    | digital LDO input                                                 |

| H6         | P15         | all functions configurable/AIO<4>                                 |

| H7         | AVDD3       | 3V power supply for analog IO, bg, rcosc, etc                     |

| Н8         | XC1_16M_IN  | 16M crystal input                                                 |

|            |             |                                                                   |

The information contained herein is the exclusive property of QST, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of QST.

## **CONTENTS**

| 3-Axis | Accelerometer                                                      |           |

|--------|--------------------------------------------------------------------|-----------|

| 1      | INTERNAL SCHEMATIC DIAGRAM                                         | 8         |

|        | 1.1 Internal Schematic Diagram                                     | 8         |

| 2      | SPECIFICATIONS AND I/O CHARACTERISTICS                             | 9         |

|        | 2.1 Product Specifications                                         | 9         |

|        | 2.2 Absolute Maximum Ratings                                       |           |

|        | 2.3 I/O Characteristics                                            |           |

| 3      | BASIC DEVICE OPERATION                                             |           |

|        | 3.1 Acceleration sensor                                            |           |

|        | 3.2 Power Management                                               | 11        |

|        | 3.3 Power On/Off Time                                              |           |

|        | 3.4 Communication Bus Interface I <sup>2</sup> C and Its Addresses |           |

| 4      | MODES OF OPERATION                                                 | 19        |

| •      | 4.1 Modes Transition                                               |           |

|        | 4.2 Description of Modes                                           |           |

| 5      | Functions and interrupts                                           |           |

| 3      | 5.1 STEP_INT                                                       |           |

|        | 5.2 DRDY_INT                                                       |           |

|        | 5.3 ANY MOT INT.                                                   | 14        |

|        | 5.3 ANY_MOT_INT                                                    | ۱۳        |

|        | 5.5 NO MOT INT                                                     | 1 /<br>1° |

|        | 5.5 NU_MU1_IN1                                                     | 1 /<br>12 |

|        | 5.6 RAISE_INT                                                      | l /       |

| _      | 5.7 Interrupt configuration                                        | 18        |

| 6      | I2C COMMUNICATION PROTOCOL                                         | 19        |

|        | 6.1 I <sup>2</sup> C Timings                                       |           |

| -      | 6.2 I <sup>2</sup> C R/W Operation                                 |           |

| 7      | REGISTERS                                                          |           |

|        | 7.1 Register Map                                                   | 21        |

|        | 7.2 Register Definition                                            |           |

|        | ntroduction                                                        |           |

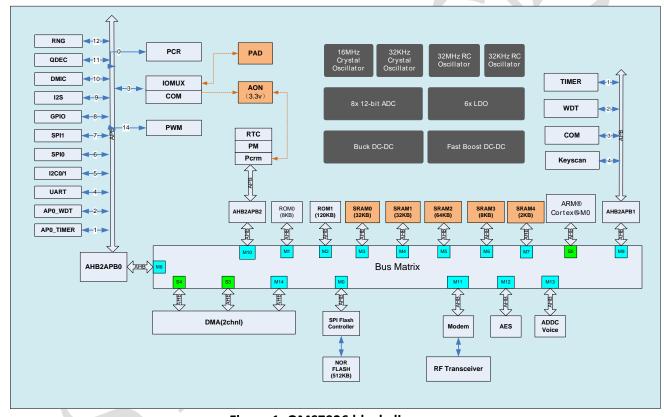

| 1      | Product Overview                                                   |           |

|        | 1.1 Block Diagram                                                  |           |

| 2      | System Blocks                                                      |           |

|        | 2.1 CPU                                                            |           |

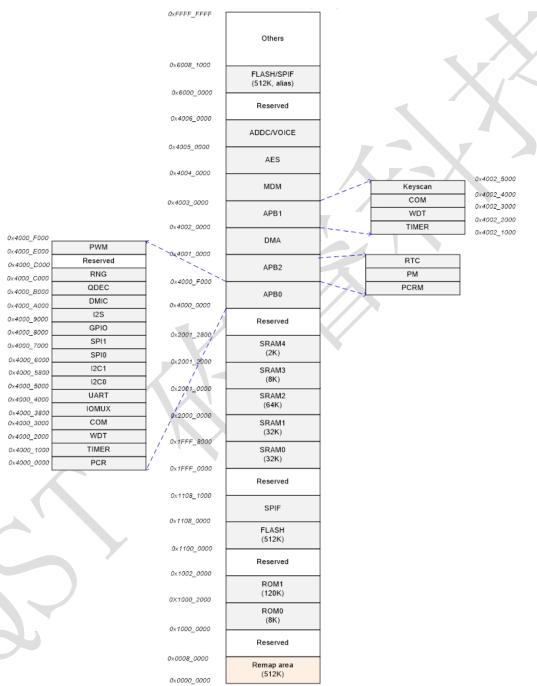

|        | 2.2 Memory                                                         |           |

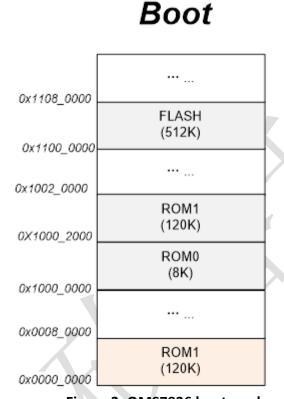

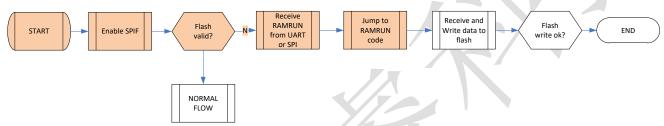

|        | 2.3 Boot and Execution Modes                                       |           |

|        | 2.4 Power, Clock and Reset (PCR)                                   |           |

|        | 2.5 Power Management (POWER)                                       |           |

|        | 2.6 Low Power Features                                             |           |

|        | 2.7 Interrupts                                                     |           |

|        | 2.8 Clock Management (CLOCK)                                       | 45        |

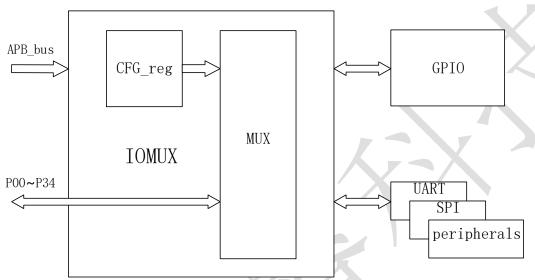

|        | 2.9 IOMUX                                                          | 46        |

|        | 2.10 GPIO                                                          | 59        |

| 3      | Peripheral Blocks                                                  | 65        |

|        | 3.1 2.4GHz Radio                                                   | 65        |

|        | 3.2 Timer/Counters (TIMER)                                         |           |

|        | 3.3 Real Time Counter (RTC)                                        |           |

|        | 3.4 AES-ECB Encryption (ECB)                                       |           |

|        | 3.5 Random Number Generator (RNG)                                  |           |

|        | 3.6 Watchdog Timer (WDT)                                           |           |

|        | 3.7 SPI (SPI)                                                      |           |

|        |                                                                    |           |

Title: QMS7926 Datasheet

Rev: A

|         | 3.8         | I2C (I2c0, I2c1 Two Independent Instances)                               | 80  |

|---------|-------------|--------------------------------------------------------------------------|-----|

|         | 3.9         | I2S                                                                      |     |

|         | 3.10        | UART (UART)                                                              |     |

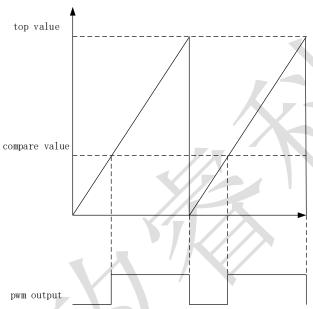

|         | 3.11        | Pulse Width Modulation (PWM)                                             |     |

|         | 3.12        | Quadrature Decoder (QDEC)                                                |     |

|         | 3.13        | Key Scan (KSCAN)                                                         |     |

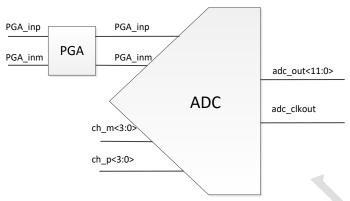

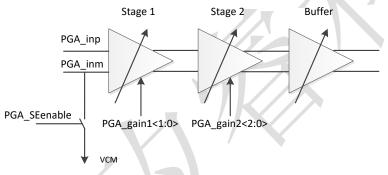

|         | 3.14        | Analog to Digital Converter (ADC) with Programmable Gain Amplifier (PGA) | 13  |

| 4       | Absolute    | e Maximum Ratings                                                        | 13  |

| 5       | Operatir    | g Conditions                                                             | 138 |

| 6       | Radio T     | ransceiver                                                               | 139 |

|         | 6.1         | Radio Current Consumption                                                | 139 |

|         | 6.2         | Transmitter Specification                                                | 139 |

|         | 6.3         | Receiver Specification                                                   | 139 |

|         | 6.4         | RSSI Specifications                                                      |     |

| 7       | Glossary    | 1                                                                        | 143 |

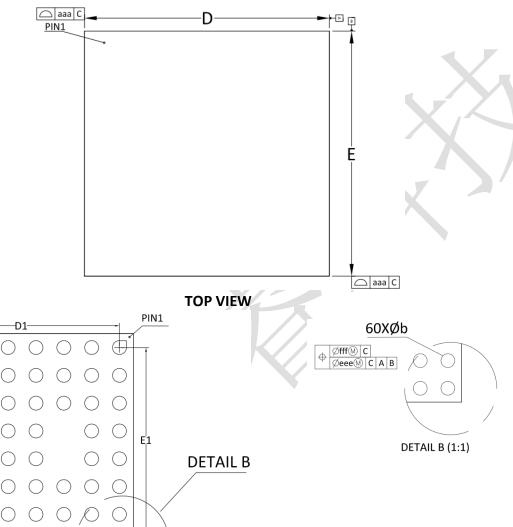

| Package | dimension   | ns.                                                                      | 144 |

| Orderin | g informat  | ion                                                                      | 145 |

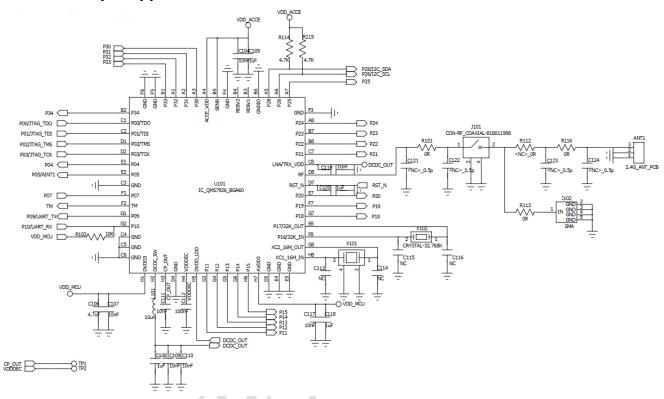

| Sample  | Application | on and Lavout Guide                                                      | 146 |

| -       | 1.1         | Sample Application                                                       | 146 |

|         | 1.2         | Layout Guide                                                             | 140 |

Title: QMS7926 Datasheet

Rev: A

# **3-Axis Accelerometer**

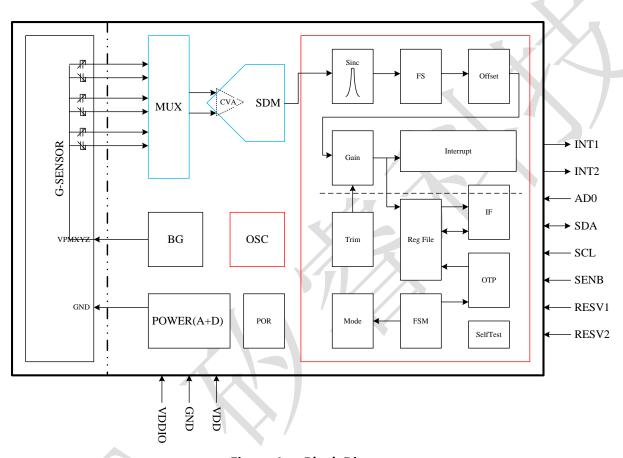

#### 1 INTERNAL SCHEMATIC DIAGRAM

## 1.1 Internal Schematic Diagram

Figure 1. Block Diagram

## Table 1. Block Function

| Block                                              | Function                                                       |  |

|----------------------------------------------------|----------------------------------------------------------------|--|

| Transducer                                         | 3-axis acceleration sensor                                     |  |

| CVA Charge-to-Voltage amplifier for sensor signals |                                                                |  |

| Interrupt                                          | Digital interrupt engine, to generate interrupt signal on data |  |

|                                                    | conversion, and motion function                                |  |

| FSM                                                | Finite state machine, to control device in different mode      |  |

| I <sup>2</sup> C/SPI                               | Interface logic data I/O                                       |  |

| OSC                                                | Internal oscillator for internal operation                     |  |

| Power                                              | Power block, including LDO                                     |  |

The information contained herein is the exclusive property of QST, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of QST.

$8\ /\ 148$

Title: QMS7926 Datasheet

Rev: A

# 2 SPECIFICATIONS AND I/O CHARACTERISTICS

# 2.1 Product Specifications

Table 2. Specifications (\* Tested and specified at 25°C and 3.0V VDD except stated otherwise.)

| Parameter                     | Conditions                                                                                           | Min  | Тур       | Max | Unit            |

|-------------------------------|------------------------------------------------------------------------------------------------------|------|-----------|-----|-----------------|

| Supply voltage VDD            | VDD, for internal blocks                                                                             | 1.71 | 3.3       | 3.6 | V               |

| I/O voltage VDDIO             | VDDIO, for IO only                                                                                   | 1.71 | 3.3       | VDD | V               |

| Standby current               | VDD and VDDIO on                                                                                     |      | 1         |     | μΑ              |

|                               | ODR=268 Hz                                                                                           |      | 50        |     |                 |

|                               | ODR=134 Hz                                                                                           |      | 25.3      |     | 21'             |

| Lave marriage arrangement     | ODR=67 Hz                                                                                            |      | 12.9      |     | μΑ              |

| Low power current             | ODR=33.6 Hz                                                                                          |      | 6.7       |     | 1               |

|                               | ODR=13.4 Hz                                                                                          |      | 2.9       |     |                 |

|                               | ODR=6.7 Hz                                                                                           |      | 1.7       |     |                 |

|                               | ODR=32.5 Hz                                                                                          |      | 100       |     |                 |

| Lavoration account            | ODR=21.6 Hz                                                                                          | 一人   | 83.3      |     | μΑ              |

| Low noise current             | ODR=13 Hz                                                                                            |      | 50        |     |                 |

|                               | ODR=6.5 Hz                                                                                           |      | 25        |     |                 |

| BW                            | Programmable bandwidth                                                                               |      | 0.16~168  |     | Hz              |

| Data output rate<br>(ODR)     | 2*BW                                                                                                 |      | 0.32~336  |     | Samples<br>/sec |

| Startup time                  | From the time when VDD reaches to 90% of final value to the time when device is ready for conversion |      | 2         |     | ms              |

| Wakeup time                   | From the time device enters into active mode to the time device is ready for conversion              |      | 1         |     | ms              |

| Operating temperature         | <b>Y</b>                                                                                             | -40  |           | 85  | °C              |

| Acceleration Full             |                                                                                                      |      | ±2/±4/±8/ |     | ~               |

| Range                         |                                                                                                      |      | ±16/±32   |     | g               |

|                               | FS=±2g                                                                                               |      | 4096      |     |                 |

|                               | FS=±4g                                                                                               |      | 2048      |     | ICD/~           |

| Sensitivity                   | FS=±8g                                                                                               |      | 1024      |     | LSB/g           |

|                               | FS=±16g                                                                                              |      | 512       |     |                 |

|                               | FS=±32g                                                                                              |      | 256       |     |                 |

| Sensitivity Temperature Drift | FS=±2g, Normal VDD Supplies                                                                          |      | ±0.02     |     | %/°C            |

| The in | nformation contained herein is the exclusive property of QST, and shall not be distributed, |

|--------|---------------------------------------------------------------------------------------------|

| reprod | duced, or disclosed in whole or in part without prior written permission of QST.            |

Title: QMS7926 Datasheet

Rev: A

| Parameter              | Conditions                      | Min | Тур  | Max | Unit   |

|------------------------|---------------------------------|-----|------|-----|--------|

| Sensitivity tolerance  | Gain accuracy                   |     | ±4   |     | %      |

| Zero-g offset          | FS=±2g, Normal VDD Supplies     |     | ±80  |     | mg     |

| Zero-g offset          | FC_+2g Normal VDD Supplies      |     | 13   |     | 1°C    |

| Temperature Drift      | FS=±2g, Normal VDD Supplies     |     | ±2   |     | mg/°C  |

| Noise density          | FS=±2g, run state               |     | 200  |     | μg/√Hz |

| Nonlinearity           | FS=±2g, Best fit straight line, |     | ±0.5 |     | %FS    |

| Cross Axis Sensitivity |                                 |     | 1    |     | %      |

## 2.2 Absolute Maximum Ratings

Table 3. Absolute Maximum Ratings (Tested at 25°C except stated otherwise.)

| Parameters          | Condition        | Min  | Max   | Units      |

|---------------------|------------------|------|-------|------------|

| VDD                 |                  | -0.3 | 5.4   | V          |

| VDDIO               |                  | -0.3 | 5.4   | V          |

| ESD                 | НВМ              |      | 2     | kV         |

| Shock Immunity      | Duration < 200μS |      | 10000 | g          |

| Storage temperature |                  | -50  | 150   | $^{\circ}$ |

## 2.3 I/O Characteristics

Table 4. I/O Characteristics

| Parameter     | Symbol            | Pin      | Condition      | Min.  | TYP. | Max.  | Unit     |

|---------------|-------------------|----------|----------------|-------|------|-------|----------|

| Voltage Input | \/1               | SDA SCI  |                | 0.7*V |      | VDDIO | ٧        |

| High Level 1  | V <sub>IH</sub> 1 | SDA, SCL |                | DDIO  |      | +0.3  | ٧        |

| Voltage Input | V <sub>IL</sub> 1 | SDA, SCL | ~ /            | -0.3  |      | 0.3*V | <b>V</b> |

| Low Level 1   | AILT              | SDA, SCL |                | -0.5  |      | DDIO  | V        |

| Voltage       |                   | INT1,    | Output Current | 0.8*V |      |       |          |

| Output High   | Vон               | INT2     | ≥-100µA        | DDIO  |      |       | V        |

| Level         |                   | IIVIZ    | 2-100μΑ        | סוסס  |      |       |          |

| Voltage       |                   | INT1,    | Output Current |       |      |       |          |

| Output Low    | VoL               | INT2,    | ≤100μA(INT)    |       |      | 0.2*V | V        |

|               | VOL               | SDA      | Output Current |       |      | DDIO  | V        |

| Level         |                   | SUA      | ≤1mA (SDA)     |       |      |       |          |

#### 3 BASIC DEVICE OPERATION

#### 3.1 Acceleration sensor

The acceleration sensor circuit consists of tri-axial sensors and application specific support circuits to measure the acceleration of device. When a DC power supply is applied to the sensor,

| The information contained herein is the exclusive property of QST, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of QST. | 10 / 148 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

Title: QMS7926 Datasheet

Rev: A

the sensor converts any accelerating incident in the sensitive axis directions to charge output.

#### 3.2 Power Management

Device has two power supply pins. VDD is the main power supply for all of the internal blocks, including analog and digital. VDDIO is a separate power supply, for digital interface only.

The device contains a power-on-reset generator. It generates reset pulse as power on, which can load the register's default value, for the device to function properly.

To make sure the POR block functions well, we should have such constrains on the timing of VDD and VDDIO.

The device should turn-on both power pins in order to operate properly. When the device is powered on, all registers are reset by POR, then the device transits to the standby mode and waits for further commends.

Table 6 provides references for four power states.

Table 6. Power States

| Power State | VDD          | VDDIO       | Power State description                            |  |  |  |  |  |  |

|-------------|--------------|-------------|----------------------------------------------------|--|--|--|--|--|--|

| 1           | 0V           | 0V          | Device Off, No Power Consumption                   |  |  |  |  |  |  |

|             |              |             | Not allowed. User need to make sure that VDDIO     |  |  |  |  |  |  |

| 2           | 0V           | 1.71V~3.6V  | is less than VDD. Otherwise, there will be leakage |  |  |  |  |  |  |

|             |              | $\sim$      | from VDDIO to VDD through internal ESD devices     |  |  |  |  |  |  |

| 3           | 1.71V~3.6V   | 0V          | Device Off, Same Current as Standby Mode           |  |  |  |  |  |  |

| 4           | 1 711/~2 61/ | 1 711/~\/DD | Device On, Normal Operation Mode, Enters           |  |  |  |  |  |  |

| 4           | 1.71V~3.6V   | 1.71V~VDD   | Standby Mode after POR                             |  |  |  |  |  |  |

#### 3.3 Power On/Off Time

Device has two power supply pins and two ground pins. VDD is the main power supply for all of the internal blocks, including analog and digital. VDDIO is a separate power supply, for digital interface only. GND is 0V supply for all of internal blocks, and GNDIO for digital interface.

There is no limitation on the voltage levels of VDD and VDDIO relative to each other, as long as they are within operating range.

The device contains a power-on-reset generator. It generates reset pulse as power on, which can load the register's default value, for the device to function properly.

| The information contained herein is the exclusive property of QST, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of QST. | 11 / 148 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

Title: QMS7926 Datasheet

Rev: A

To make sure the POR block functions well, we should have such constrains on the timing of VDD.

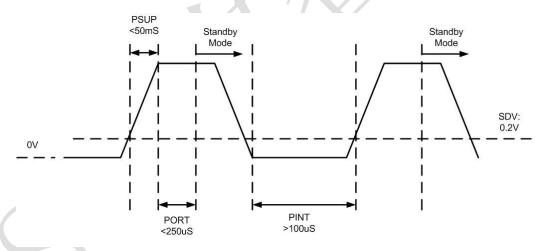

The power on/off time related to the device is in Table 7

Table 7. Time Required for Power On/Off

| Parameter                 | Symbol | Condition                                                                                                           | Min. | Тур. | Max. | Unit |

|---------------------------|--------|---------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| POR<br>Completion<br>Time | PORT   | Time Period After VDD and VDDIO at Operating Voltage to Ready for I <sup>2</sup> C Commend and Analogy Measurement. |      |      | 250  | μς   |

| Power off<br>Voltage      | SDV    | Voltage that Device<br>Considers to be Power<br>Down.                                                               | 1    |      | 0.2  | V    |

| Power on<br>Interval      | PINT   | Time Period Required for Voltage Lower Than SDV to Enable Next POR                                                  | 100  |      |      | μs   |

| Power on Time             | PSUP   | Time Period Required for Voltage from SDV to 90% of final value                                                     |      |      | 50   | ms   |

Figure 9. Power On/Off Timing

#### 3.4 Communication Bus Interface I<sup>2</sup>C and Its Addresses

This device will be connected to a serial interface bus as a slave device under the control of a master device, such as the processor. Control of this device is carried out via I<sup>2</sup>C.

This device is compliant with  $I^2C$  -Bus Specification, document number: 9398 393 40011. As an  $I^2C$  compatible device, this device has a 7-bit serial address and supports  $I^2C$  protocols. This device

| The information contained herein is the exclusive property of QST, and shall not be distributed, | 12 / 148 |

|--------------------------------------------------------------------------------------------------|----------|

| reproduced, or disclosed in whole or in part without prior written permission of QST.            | 12 / 148 |

Title: QMS7926 Datasheet

Rev: A

supports standard and fast speed modes, 100 kHz and 400 kHz, respectively. External pull-up resistors are required to support all these modes.

There are two I<sup>2</sup>C addresses selected by connecting pin 1 (AD0) to GND or VDDIO. The first six MSB are hardware configured to "001001" and the LSB can be configured by AD0.

Table 8. I<sup>2</sup>C Address Options

| AD0 (pin 1)    | I <sup>2</sup> C Slave Address(HEX) | I <sup>2</sup> C Slave Address(BIN) |

|----------------|-------------------------------------|-------------------------------------|

| Connect to GND | 12                                  | 0010010                             |

#### 4 MODES OF OPERATION

#### 4.1 Modes Transition

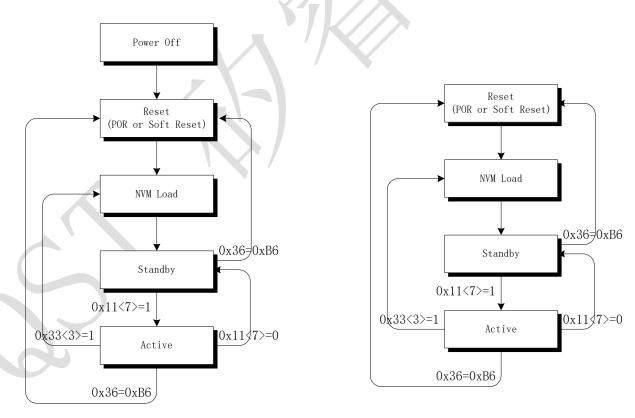

QMA7981 has two different operational modes, controlled by register (0x11), MODE\_BIT. The main purpose of these modes is for power management. The modes can be transited from one to another, as shown below, through I<sup>2</sup>C commands. The default mode after power-on is standby mode.

Figure 10. Basic operation flow after power-on

Figure 11. The work mode transferring

The information contained herein is the exclusive property of QST, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of QST.

Title: QMS7926 Datasheet

Rev: A

The default mode after power on is standby mode. Through I<sup>2</sup>C instruction, device can switch between standby mode and active mode. With SOFTRESET by writing 0xB6 into register 0x36, all of the registers will get default values. SOFTRESET can be done both in active mode and in standby mode. Also, by writing 1 in NVM\_LOAD (0x33<3>) when device is in active mode, the NVM related image registers will get default value from NVM, however, other registers will keep the values of their own.

#### 4.2 Description of Modes

#### 4.2.1 Active Mode

In active mode, the ADC digitizes the charge signals from transducer, and digital signal processor conditions these signals in digital domain, processes the interrupts, and send data to Data registers (0x01~0x06).

#### 4.2.2 Standby Mode

In standby mode, most of the blocks are off, while device is ready for access through I<sup>2</sup>C. Standby mode is the default mode after power on or soft reset. Device can enter into this mode by set the soft reset register (0x36) to 0xB6 or set the MODE\_BIT (0x11<7>) to logic 0.

Besides the above two modes, the device also contains NVM loading state. This state is used to reset the value of the NVM related image registers. There are two bits related to this state. When NVM\_LOAD (0x33<3>) is set to 1, NVM loading starts. When the device is in NVM loading state, NVM\_RDY (0x33<2>) is set to logic 0 by device. After NVM loading is finished, NVM\_RDY (0x33<2>) is set back to logic 1 by device, and NVM\_LOAD is reset to 0 by device automatically. NVM loading can only happen when NVM\_LOAD is set to 1 in active mode. If the user sets this NVM\_LOAD bit to 1 in standby mode, the device will not take the action until it enters into active state by setting MODE\_BIT (0x11<7>) to logic 1.

After loading NVM, the device will enter into standby mode directly.

The loading time for NVM is about 100uS.

#### 5 Functions and interrupts

ASIC support interrupts, such as STEP\_INT, DRDY\_INT, ANY\_MOT\_INT, SIG\_MOT\_INT, NO\_MOT\_INT, RAISE\_INT, etc.

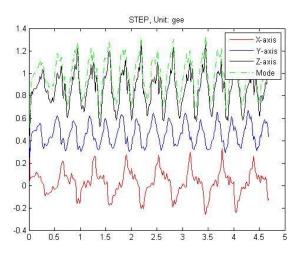

#### 5.1 STEP\_INT

The STEP/STEP\_QUIT detect that the user is entering/exiting step mode. When the user enter into step mode, at least one axis sensor data will vary periodically, by numbering the variation periods the step counter can be calculated.

The information contained herein is the exclusive property of QST, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of QST.

Title: QMS7926 Datasheet

Rev: A

Figure 12. STEP/STEP QUIT

Median data (max+min) /2 is called dynamic threshold, the max and min data can be updated by certainly samples, the sample number can be set by register STEP\_SAMPLE\_CNT(0x12<6:0>). When the sensor data decreasing (or increasing) through the dynamic threshold, a user run step is detected.

Register STEP\_PRECISION (0x13<6:0>) is used as threshold when updating the new collected sensor data. Sensor data below the threshold will be discarded, this helps removing unstable variations causing failed detection.

The run step event happened at certain interval timing. All of the events outside the timing window will not be regarded as a run step and the step counter will not counted. The timing window can be set by register STEP\_TIME\_UP(0x15) and STEP\_TIME\_LOW(0x14), the conversion ODR numbers ranged from STEP\_TIME\_LOW \*ODR to 8\* STEP\_TIME\_UP\*ODR .

STEP\_COUNT\_PEAK<2:0> is used to set a fixed peak value for step detection, 0.05G~0.4G can be set. STEP\_COUNT\_P2P<2:0> is used to set a peak to peak threshold for step detection, 0.3G~1G can be set.

To remove unstable variation which will cause false STEP event detection, the step counter considers steps as valid step events only after some continuous steps detected; the start threshold can be set by 0x1F<7:5>. Also, the step counter register STEP\_CNT<23:0> ({0x0E,0x08,0x07}) will be updated immediately by the setting number, and interrupt STEP is also generated.

The related interrupt status bit is STEP\_INT (0x0A<3>) and SIG\_STEP (0x0A<6>). When the interrupt is generated, the value of STEP\_INT will be set to logic 1, which will be cleared after the interrupt status register is read by user. STEP\_IEN/SIG\_STEP\_IEN (0x16<3>/0x16<6>) is the enable bit for the STEP\_INT/SIG\_STEP\_INT. Also, to get this interrupt on PIN\_INT1 and/or PIN\_INT2, we need to set INT1\_STEP (0x19<3>)/INT1\_SIG\_STEP (0x19<6>) or INT2\_STEP (0x1B<3>) /INT2\_SIG\_STEP (0x1B<6>) to logic 1, to map the interrupt to the interrupt PINs.

The information contained herein is the exclusive property of QST, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of QST.

Title: QMS7926 Datasheet

Rev: A

#### 5.2 DRDY\_INT

The width of the acceleration data is 14 bits, in two's complement representation. The data of each axis is split into 2 parts, the MSB part (one byte contains bit 13 to bit 6) and the LSB part (one byte contains bit 5 to bit 0). Reading data should start with LSB part. When user is reading the LSB byte of data, to ensure the integrity of the acceleration data, the content of MSB can be locked, by setting SHADOW\_DIS (0x21<6>) to logic 0. This lock function can be disabled by setting SHADOW\_DIS to logic 1. Without lock, the MSB and LSB content will be updated by new value immediately. The bit NEW\_DATA in the LSB byte is the flag of the new data. If new data is updated, this NEW\_DATA flag will be 1, and will be cleared when corresponding MSB or LSB is read by user.

Also, the user should note that even with SHADOW\_DIS=0, the data of 3 axes are not guaranteed from the same time point.

The device supports four different acceleration measurement ranges. The range is setting through RANGE (0x0F<3:0>), and the details as following:

| RANGE  | Acceleration range | Resolution |

|--------|--------------------|------------|

| 0001   | 2g                 | 244ug/LSB  |

| 0010   | 4g                 | 488ug/LSB  |

| 0100   | 8g                 | 977ug/LSB  |

| 1000   | 16g                | 1.95mg/LSB |

| 1111   | 32g                | 3.91mg/LSB |

| Others | 2g                 | 244ug/LSB  |

The interrupt for the new data serves for the synchronous data reading for the host. It is generated after storing a new value of z-axis acceleration data into data register. This interrupt will be cleared automatically when the next data conversion cycle starts, and the interrupt will be effective about 64\*MCLK, and automatically cleared.

The interrupt mode for the new data is fixed to be non-latched.

#### 5.3 ANY MOT INT

Any motion Any motion detection uses slope between two successive data to detect the changes in motion. It generates interrupt when a preset threshold ANY\_MOT\_TH (0x2E) is exceeded.

The time difference between two successive data depends on the output data rate (ODR).

$$Slope(t1) = (acc(t1) - acc(t0)) * ODR$$

The any motion detection criteria are fulfilled and interrupt is generated if any of enabled channels exceeds ANY\_MOT\_TH for ANY\_MOT\_DUR (0x2C<1:0>) consecutive times.

The information contained herein is the exclusive property of QST, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of QST.

Title: QMS7926 Datasheet

Rev: A

As long as all the enabled channels data fall or stay below ANY\_MOT\_TH for ANY\_MOT\_DUR consecutive times, the interrupt will be reset unless the interrupt signal is latched.

The any motion detection engine will send out the signals of axis which triggered the interrupt (ANY\_MOT\_FIRST\_X (0x09<0>), ANY\_MOT\_FIRST\_Y (0x09<1>), ANY\_MOT\_FIRST\_Z (0x09<2>)) and the sign of the motion (ANY\_MOT\_SIGN (0x09<3>))

#### 5.4 SIG\_MOT\_INT

A significant motion is a motion due to a change in user location.

The algorithm is as following:

- 1) Look for movement, same setting as any motion detection

- 2) If movement detected, sleep for T\_Skip (0x2F<3:2>)

- 3) Look for movement

- a) If no movement detected within T Proof (0x2F<5:4>), go back to 1

- b) If movement detected, report a significant movement, and generate the interrupt

The significant motion detection and any motion detection are exclusive, user can select either one through SIG MOT SEL (0x2F<0>).

If significant motion is detected, the engine will set SIG MOT INT (0x0A<0>).

#### 5.5 NO\_MOT\_INT

No-motion interrupt is generated if the slope (absolute value of acceleration difference) on all selected axes is smaller than the programmable threshold for a programmable time. Figure shows the timing for the no-motion interrupt. Register (0x2C) NO\_MOT\_DUR defines the delay times before the no-motion interrupt is generated. Table lists the delay times adjustable with register (0x2C) NO\_MOT\_DUR.

The no-motion interrupt is enabled per axis by writing logic 1 to bits (0x18) NO\_MOTION\_EN\_X, (0x18) NO\_MOTION\_EN\_Y, and (0x18) NO\_MOTION\_EN\_Z, respectively. The no-motion threshold is set through the (0x2D) NO\_MOT\_TH register. The meaning of an LSB of (0x2D) NO\_MOT\_TH depends on the selected g-range: it corresponds to 3.91mg in 2g-range (7.81mg in 4g-range, 15.6mg in 8g-range, 31.25mg in 16g-range, 62.5mg in 32g-range). Therefore the maximum value is 996mg in 2g-range (2g in 4g-range, 4g in 8g-range, 8g in 16g-range, and 16g in 32g-range). The time difference between the successive acceleration samples depends on the selected ODR and equates to 1/ODR.

#### 5.6 RAISE\_INT

Raise wake algorithm is used to detect the action of raise hand (or hand down). The interrupt is enabled by writing logic 1 to bits (0X16[1]) RAISE\_EN, (0X16[2]) HD\_EN. User can adjust the sensitivity through the registers. The register RAISE\_WAKE\_SUM\_TH(0X2A[5:0]) defines the

The information contained herein is the exclusive property of QST, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of QST.

Title: QMS7926 Datasheet

Rev: A

strength of hand action (raise and down). The register RAISE\_DIFF\_TH(0X2A[7:6],0X2B[1:0]) defines the differential values of twice actions, when the hand behavior almost done the differential value will be smaller and we can use this register to set the threshold. RAISE\_WAKE\_PERIOD and RAISE\_WAKE\_TIMEOUT\_TH define the duration of the total hand action.

#### 5.7 Interrupt configuration

The device has the above 3 interrupt engines. Each of the interrupts can be enabled and configured independently. If the trigger condition of the enabled interrupt fulfilled, the corresponding interrupt status bit will be set to logic 1, and the mapped interrupt pin will be activated. The device has two interrupt PINs, INT1 and INT2. Each of the interrupts can be mapped to either PIN or both PINs.

The interrupt status registers  $INT_ST(0x09^{\circ}0x0d)$  will update when a new data word is written into the data registers. If an interrupt is disabled, the related active interrupt status bit is disabled immediately.

When interrupt condition is fulfilled, related bit of interrupt will be set, until the associated interrupt condition is no more valid. Read operation to related register will also clear the register.

Device supports 2 interrupt modes, non-latched, and latched mode. The interrupt modes are set through LATCH\_INT (0x21<0>).

In non-latched mode, the mapped interrupt pin will be set and/or cleared same as associated interrupt register bit. Also, the mapped interrupt pin can be cleared with read operation to any of the INT ST(0x09~0x0d).

Exception to this is the new data interrupt and step interrupt, which are automatically reset after a fixed time ( $T_pulse = 64/MCLK$ ), no matter LATCH\_INT (0x21<0>) is set to 0 or 1.

In latched mode, the clearings of mapped pins are determined by INT\_RD\_CLR (0x21<7>). If the condition for trigging the interrupt still holds, the interrupt status will be set again with the next change of the data registers.

Mapping the interrupt pins can be set by INT MAP (0x19~0x1B).

The electrical interrupt pins can be set INT\_PIN\_CONF (0x20<3:0>). The active logic level can be set to 1 or 0, and the interrupt pin can be set to open-drain or push-pull.

The information contained herein is the exclusive property of QST, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of QST.

| ₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩ | Document #: | 13-52-18 | Title: | QMS7926 Datasheet | Rev: A |

|----------------------------------------|-------------|----------|--------|-------------------|--------|

|                                        |             |          |        |                   |        |

## **6 I2C COMMUNICATION PROTOCOL**

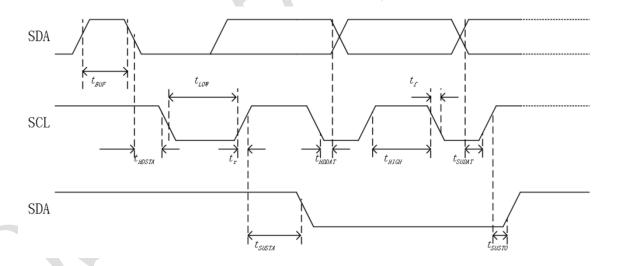

# 6.1 I<sup>2</sup>C Timings

Table 9 and Figure 11 describe the  $I^2C$  communication protocol times

Table 9. I<sup>2</sup>C Timings

| Parameter             | Symbol             | Condition    | Min. | Тур. | Max. | Unit |

|-----------------------|--------------------|--------------|------|------|------|------|

| SCL Clock             | $f_{scl}$          |              | 0    | V    | 400  | kHz  |

| SCL Low Period        | $t_{low}$          |              | 1    |      |      | μs   |

| SCL High Period       | $t_{high}$         |              | 1    |      |      | μs   |

| SDA Setup Time        | t <sub>sudat</sub> |              | 0.1  | V    |      | μs   |

| SDA Hold Time         | t <sub>hddat</sub> |              | 0    |      | 0.9  | μs   |

| Start Hold Time       | t <sub>hdsta</sub> |              | 0.6  |      |      | μs   |

| Start Setup Time      | t <sub>susta</sub> |              | 0.6  |      |      | μs   |

| Stop Setup Time       | $t_{susto}$        |              | 0.6  |      |      | μs   |

| New Transmission Time | t <sub>buf</sub>   |              | 1.3  |      |      | μs   |

| Rise Time             | $t_{r}$            | <b>X</b> -/- |      |      |      | μs   |

| Fall Time             | $t_{f}$            |              |      |      |      | μs   |

Figure 13. I<sup>2</sup>C Timing Diagram

# 6.2 I<sup>2</sup>C R/W Operation

#### 6.2.1 Abbreviation

| The information contained herein is the exclusive property of QST, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of QST. | 19 / 148 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

Title: QMS7926 Datasheet

Rev: A

#### Table 10. Abbreviation

| SACK | Acknowledged by slave      |

|------|----------------------------|

| MACK | Acknowledged by master     |

| NACK | Not acknowledged by master |

| RW   | Read/Write                 |

#### 6.2.2 Start/Stop/Ack

START: Data transmission begins with a high to transition on SDA while SCL is held high. Once I<sup>2</sup>C transmission starts, the bus is considered busy.

STOP:STOP condition is a low to high transition on SDA line while SCL is held high.

ACK: Each byte of data transferred must be acknowledged. The transmitter must release the SDA line during the acknowledge pulse while the receiver mush then pull the SDA line low so that it remains stable low during the high period of the acknowledge clock cycle.

NACK: If the receiver doesn't pull down the SDA line during the high period of the acknowledge clock cycle, it's recognized as NACK by the transmitter.

#### 6.2.3 I<sup>2</sup>C Write

I<sup>2</sup>C write sequence begins with start condition generated by master followed by 7 bits slave address and a write bit (R/W=0). The slave sends an acknowledge bit (ACK=0) and releases the bus. The master sends the one byte register address. The slave again acknowledges the transmission and waits for 8 bits data which shall be written to the specified register address. After the slave acknowledges the data byte, the master generates a stop signal and terminates the writing protocol.

Table 11. I<sup>2</sup>C Write

|      | ۱ W ۱ و٠ |   |   |   |   |   |   |                  |        |   | Register Address |   |   |   |     |        |   |   |   |   | Da | ta  |     |   |   |   |   |

|------|----------|---|---|---|---|---|---|------------------|--------|---|------------------|---|---|---|-----|--------|---|---|---|---|----|-----|-----|---|---|---|---|

| STAI | -1.      |   |   |   |   |   | W | $\triangleright$ | (0x11) |   |                  |   |   |   | SAC | (0x80) |   |   |   |   |    | SAC | STO |   |   |   |   |

| RT   | 0 0      | 1 | 0 | 0 | 1 | 0 | 0 | 웃                | 0      | 0 | 0                | 1 | 0 | 0 | 0   | 1      | × | 1 | 0 | 0 | 0  | 0   | 0   | 0 | 0 | X | P |

#### 6.2.4 I<sup>2</sup>C Read

$I^2C$  write sequence consists of a one-byte  $I^2C$  write phase followed by the  $I^2C$  read phase. A start condition must be generated between two phase. The  $I^2C$  write phase addresses the slave and sends the register address to be read. After slave acknowledges the transmission, the master generates again a start condition and sends the slave address together with a read bit (R/W=1). Then master releases the bus and waits for the data bytes to be read out from slave. After each data byte the master has to generate an acknowledge bit (ACK = 0) to enable further data transfer.

The information contained herein is the exclusive property of QST, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of QST.

Title: QMS7926 Datasheet

Rev: A

A NACK from the master stops the data being transferred from the slave. The slave releases the bus so that the master can generate a STOP condition and terminate the transmission.

The register address is automatically incremented and more than one byte can be sequentially read out. Once a new data read transmission starts, the start address will be set to the register address specified in the current I<sup>2</sup>C write command.

Table 12. I<sup>2</sup>C Read

| Slave Address |      |     |     |    |     |     | R<br>W | ٧S     | Register Address |   |                |   |   |      |   |   |   |           |                |   |   |   |      |      |   |   |    |     |

|---------------|------|-----|-----|----|-----|-----|--------|--------|------------------|---|----------------|---|---|------|---|---|---|-----------|----------------|---|---|---|------|------|---|---|----|-----|

| START         | 0    | 0   | 1   | 0  | 0   | 1   | 0      | 0      | SACK             | 0 | 0              | 0 | 0 | 0    | 0 | 0 | 0 | CK        | 7              |   |   |   |      | Z    | 7 |   |    | ) / |

| START         |      | Sla | ive | Ac | ddr | ess |        | R<br>W | SA               |   | Data<br>(0x00) |   |   |      |   |   |   |           | Data<br>(0x01) |   |   |   |      |      |   |   |    |     |

| \RT           | 0    | 0   | 1   | 0  | 0   | 1   | 0      | 1      | SACK             | 0 | 0              | 0 | 0 | 0    | 0 | 1 | 0 | MACK      | 0              | 0 | 0 | 0 | 0    | 0    | 0 | 0 |    |     |

| MACK          | Data |     |     |    |     |     |        |        |                  |   |                |   |   | MACK |   |   |   | Da<br>(0x |                |   |   |   | NACK | STOP |   |   |    |     |

| CK            | 0    | 0   | 0   | 0  | 0   | 0   | 1      | 0      | CK               |   |                |   |   |      |   |   |   |           | 0              | 0 | 0 | 0 | 0    | 0    | 0 | 0 | CK | ЭP  |

#### 7 REGISTERS

#### 7.1 Register Map

The table below provides a list of the 8-bit registers embedded in the device and their respective function and addresses

Table 13. Register Map

The information contained herein is the exclusive property of QST, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of QST.

Title: QMS7926 Datasheet

Rev: A

| Add.         | Name        | bit7                                  | bit6                                    | bit5           | bit4                | bit3                                      | bit2                 | bit1            | bit0                         | R/W      | DEF      |

|--------------|-------------|---------------------------------------|-----------------------------------------|----------------|---------------------|-------------------------------------------|----------------------|-----------------|------------------------------|----------|----------|

| 0x3F         | Name        | DILL                                  |                                         | : WAKE PERIOD[ |                     | D1 (2                                     | RAISE WAKE TII       |                 | DICO                         | RW       | 02       |

|              | RAISE CFG   |                                       | KAIDE                                   | _WAKE_FEKTODE  | RAISE WAKE TI       | שבחוד דנו[ק.ה]                            | KAISE_WARE_III       | MECOLITIES      | -                            | RW       | 00       |

|              | S_RESET     |                                       |                                         |                | SOFTRESE            |                                           |                      |                 |                              | RW       | 00       |

| 0x35         | o_RESEI     |                                       |                                         |                | RAISE_WAKE_         |                                           |                      |                 |                              | RW       | 81       |

| 0x34         |             |                                       | YZ_TH_SEL[2:0]                          |                | KHIDE_#HKE_         | ERIOD[1.0]                                | Y_TH[4:0]            |                 |                              | RW       | 9D       |

|              | ST          | SELFTEST BIT                          | 12_111_566[2.0]                         |                |                     |                                           | SELFTEST_SIGN        | BP_AXIS :       | STRP(1:0)                    | RW       | 00       |

| 0x31         | 51          | DEEL TEST_BIT                         |                                         |                |                     |                                           | DEEPTEDT_DIGIT       | DI_HXIU_        | 51E1 (1.0)                   | RW       | 00       |

|              | RST MOT     | MO BP CO                              | STEP BP CO                              |                | LOW RST N           | HIGH RST N                                | NO MOT RST N         | SIG MOT RST N   | ANY MOT RST N                |          | 1F       |

| 0x2F         |             | DI00                                  | 0101_01_00                              | SIG MOT T      | PROOF<1:0>          |                                           | SKIP<1:0>            | DEC_MOT_NOT_N   | SIG MOT SEL                  | RW       | 00       |

| 0x2E         |             |                                       |                                         |                | ANY MOT             |                                           |                      |                 |                              | R₩       | 00       |

| 0x2D         |             |                                       |                                         |                | NO_MOT_             | TH<7:0>                                   |                      |                 |                              | R₩       | 00       |

| 0x2C         | MOT_CFG     |                                       |                                         | NO_MOT_I       | DUR<5:0>            |                                           | `                    | ANY_MOT_        | DUR<1:0>                     | R₩       | 00       |

| 0x2B         |             |                                       | HD_Z_TH[2:0]                            |                |                     | HD_X_TH[2:0]                              | `                    | RAISE_WAKE_I    | DIFF_TH[3:2]                 | R₩       | 7C       |

| 0x2A         | RAISE_CFG   | RAISE_WAKE_I                          | DIFF_TH[1:0]                            |                |                     | RAISE_WAKE_                               | SUM_TH[5:0]          |                 |                              | R₩       | D8       |

| 0x29         |             |                                       |                                         |                | OS_CUST             | _                                         |                      |                 |                              | R₩       | 00       |

| 0x28         |             |                                       |                                         |                | OS_CUST             |                                           |                      |                 |                              | R₩       | 00       |

|              | OS_CUST     |                                       |                                         |                | OS_CUST             | _                                         | <u> </u>             | <u> </u>        |                              | R₩       | 00       |

|              | INT_CFG     | INT_RD_CLR                            | SHADOW_DIS                              | DIS_I2C        | 1                   | 1                                         | 1                    | LATCH_INT_STEP  | LATCH_INT                    | R₩       | 1C       |

|              | INT_PIN_CFG | DIS_PU_SENB                           | DIS_IE_ADO                              | EN_SPI3W       | STEP_COUNT_PEAK<2>  | INT2_OD                                   | INT2_LVL             | INT1_OD         | INT1_LVL                     | R₩       | 05       |

| 0x1F         |             | STI                                   | EP_START_CNT<2                          |                | STEP_COUNT          | _PEAK<1:0>                                |                      | P_COUNT_P2P<2   | :0>                          | R₩       | A9       |

| 0x1E         | aren ara    |                                       | Z_TH                                    |                | DD THERRIAL /C      | ^\                                        | X_TH                 | [3:0]           | PM PROPE DO                  | R₩       | 66       |

| 0x1D         | STEP_CFG    | THTO NO HOT                           | 1                                       |                | EP_INTERVAL<6:      |                                           | THEO HEAR            | 1               | EN_RESET_DC                  | RW       | 00<br>62 |

| 0x1C         |             | INT2_NO_MOT                           | 1<br>INT2 SIG STEP                      | 1 1            | INT2_DATA<br>1      | INT2_LOW<br>INT2 STEP                     | INT2_HIGH            | INT2 RAISE      | INT2_ANY_MOT<br>INT2 SIG MOT | RW<br>RW | B0       |

| 0x1B<br>0x1A |             | INT1 NO MOT                           | 1                                       | 1              | INT1 DATA           | INT1 LOW                                  | INT2_HD<br>INT1 HIGH | 1 1N12_KAISE    | INT1 ANY MOT                 |          | 62       |

|              | INT_MAP     | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | INT1_SIG_STEP                           | 1              | 1                   | INT1_EOW<br>INT1_STEP                     | INT1_HD              | INT1_RAISE      | INT1_ANT_MOT                 |          | B0       |

| 0x18         | 1111_MAI    | NO MOT EN Z                           | NO MOT EN Y                             | NO MOT EN X    | 1                   | 1                                         | ANY MOT EN Z         |                 | ANY MOT EN X                 | RW       | 18       |

| 0x17         |             | 1                                     | 1                                       | 1              | INT_DATA_EN         | LOW_EN                                    | HIGH_EN_Z            | HIGH_EN_Y       | HIGH_EN_X                    | RW       | EO       |

|              | INT_EN      | 1                                     | SIG_STEP_IEN                            | 1              |                     | STEP IEN                                  | HD_EN                | RAISE_EN        | 1                            | RW<br>KW | B1<br>UV |

|              |             | _                                     |                                         |                |                     |                                           |                      |                 | -                            | •        |          |

| 0x14         |             | OTED OLD                              |                                         |                | STEP_TIME           |                                           | - ^\                 |                 |                              | R₩       | 19       |

| 0x13         | STEP CFG    | STEP_CLR<br>STEP_EN                   |                                         |                |                     | <u>PPPRECISION&lt;6</u><br>P SAMPLE CNT<6 |                      |                 |                              | RW<br>RW | 7F       |

| 0x12<br>0x11 | PM          | MODE BIT                              | 1                                       | т вете ети     | IC_SEL<1:0>         | F_SAMFLE_CNI\                             | MCLK S               | DI /2.0\        |                              | RW       | 40       |

| 0x10         |             | 1                                     | 1                                       | 1_K31B_31N     | C_SEL\1.0/          |                                           | BW<4:0>              | EL\3.0/         |                              | R₩       | E0       |

| _            | FSR         | 1                                     | 1                                       | 1              | 1                   |                                           |                      | <3:0>           |                              | RW       | FO.      |

|              | STEPCNT     | -                                     |                                         | -              | STEP_CN1            | [<23:16>                                  | KIIIIOL              |                 |                              | R        | 00       |

| 0x0D         |             |                                       |                                         |                | 5.20.,              |                                           |                      |                 |                              | R        | 00       |

| 0x0C         |             |                                       |                                         |                | HIGH_INT            | HIGH SIGN                                 | HIGH FIRST Z         | HIGH FIRST Y    | HIGH FIRST X                 | R        | 00       |

| 0x0B         |             |                                       |                                         |                | DATA INT            | LOW INT                                   |                      |                 |                              | R        | 00       |

| 0x0A         |             |                                       | SIG_STEP                                |                | _                   | STEP_INT                                  | HD_INT               | RAISE_INT       | SIG_MOT_INT                  | R        | 00       |

| 0x09         | INT_ST      | NO_MOT                                |                                         |                |                     | ANY_MOT_SIGN                              | ANY_MOT_FIRST_Z      | ANY_MOT_FIRST_Y | ANY_MOT_FIRST_X              | R        | 00       |

| 0x08         |             |                                       |                                         |                | STEP_CN             | T<15:8>                                   |                      |                 | ·                            | R        | 00       |

| 0x07         | STEPCNT     |                                       |                                         |                | STEP_CI             | T<7:0>                                    |                      |                 |                              | R        | 00       |

| 0x06         |             |                                       |                                         |                | ACC_Z               | (13:6>                                    |                      |                 |                              | R        | 00       |

| 0x05         |             |                                       |                                         | ACC_Z          | <5:0>               |                                           |                      |                 | NEWDATA_Z                    | R        | 00       |

| 0x04         |             |                                       |                                         |                | ACC_Y               | (13:6>                                    |                      | T               | 1                            | R        | 00       |

| 0x03         |             |                                       |                                         | ACC_Y          | <u>'&lt;5:0&gt;</u> |                                           |                      |                 | NEWDATA_Y                    | R        | 00       |

| 0x02         |             |                                       |                                         |                | ACC_X               | (13:6>                                    |                      | т               | 1                            | R        | 00       |

|              | DATA        |                                       |                                         |                | (<5:0>              |                                           |                      |                 | NEWDATA_X                    | R        | 00       |

| 0x00         | CHIP ID     |                                       | CHIP ID to indicate the product version |                |                     |                                           |                      |                 |                              |          | ANA      |

# 7.2 Register Definition

Register 0x00 (CHIP ID)

| Bit7    | Bit6  | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | R/W | Default |

|---------|-------|------|------|------|------|------|------|-----|---------|

| CHIP_ID | <7:0> |      |      |      |      |      |      | RW  | 0xEX    |

This register is used to identify the device

Register 0x01 ~ 0x02 (DXL, DXM)

| -6      | ,        |      |      |      |      |      |       |     |         |  |  |

|---------|----------|------|------|------|------|------|-------|-----|---------|--|--|

| Bit7    | Bit6     | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0  | R/W | Default |  |  |

| DX<5:0> |          |      |      |      |      |      | NEWD  | R   | 0x00    |  |  |

|         |          |      |      |      |      |      | ATA_X |     |         |  |  |

| DX<13:6 | DX<13:6> |      |      |      |      |      |       |     | 0x00    |  |  |

| The information contained herein is the exclusive property of QST, and shall not be distributed, |

|--------------------------------------------------------------------------------------------------|

| reproduced, or disclosed in whole or in part without prior written permission of QST.            |

Title: QMS7926 Datasheet

Rev: A

DX: **NEWDATA X:**  14bits acceleration data of x-channel. This data is in two's complement. 1, acceleration data of x-channel has been updated since last reading

0, acceleration data of x-channel has not been updated since last reading

#### Register 0x03 ~ 0x04 (DYL, DYM)

| Bit7    | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0  | R/W | Default |

|---------|------|------|------|------|------|------|-------|-----|---------|

| DY<5:0> |      |      |      |      |      |      | NEWD  | R   | 0x00    |

|         |      |      |      |      |      |      | ATA_Y |     |         |

| DY<13:6 | >    |      |      |      |      |      |       | R   | 0x00    |

DY: **NEWDATA Y:**  14bits acceleration data of y-channel. This data is in two's complement. 1, acceleration data of y-channel has been updated since last reading

0, acceleration data of y-channel has not been updated since last reading

#### Register 0x05 ~ 0x06 (DZL, DZM)

| <u> </u> |      |      | /    |      |      |      |       |     |         |

|----------|------|------|------|------|------|------|-------|-----|---------|

| Bit7     | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0  | R/W | Default |

| DZ<5:0>  |      |      |      |      |      |      | NEWD  | R   | 0x00    |

|          |      |      |      |      | 1/7  |      | ATA_Z |     |         |

| DZ<13:6  | >    |      |      |      | 1/4  |      |       | R   | 0x00    |

DZ:

14bits acceleration data of z-channel. This data is in two's complement.

**NEWDATA Z:**

1, acceleration data of z-channel has been updated since last reading

0, acceleration data of z-channel has not been updated since last reading

#### Register 0x07 ~ 0x08 (STEP CNT)

| • | Bisto: Cito | , ,,,,,, | <u> </u> | 1    |      |      |      |      |     |         |

|---|-------------|----------|----------|------|------|------|------|------|-----|---------|

|   | Bit7        | Bit6     | Bit5     | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | R/W | Default |